铜线工艺介绍

1997年9月,IBM公司宣布将从1998年开始提供以铜取代铝的芯片布线连接技术。随后大名鼎鼎的Motorola(半导体领域的先驱,孕育了非常多的知名公司)开始大批量上市铜绑定线的芯片,并取得了极大的成功。

铜绑定线代替铝绑定线是半导体产业发展历史上一个重要的里程碑。且在半导体技术发展过程中立下汗马功劳。然而在功率半导体领域,铜绑定线并没有被大量引入和应用,所占的市场份额不足1%,至今依然还面临很多工艺问题。

铜绑定线取代铝绑定线需要的一个必要条件是芯片表面金属化同样需要进行调整。因为,对于功率半导体而言,芯片表面金属化一般多采用铝。而铝材质偏软,铜偏硬,二者是无法实现直接键合的。那么是否可以改成强度更高的金属层呢?实验发现铜是非常合适的金属,而且非常适合铜线或者铜带在其表面进行互联。另外,功率半导体一般采用的直径更大的绑定线,这就要求表面铜金属化需要一定的厚度,也就是所谓的厚铜工艺。(厚)铜表面金属化工艺目前的几个主要问题如下:

表面铜金属化目前普遍采用的是电镀(ECD)法。铜作为一种扩散金属,具有较高的溶解度和扩散系数,可以在较低的温度下快速扩散,并且能扩散到SiO2层,进而进入Si中并在其中引入深陷阱能级,导致少数载流子寿命的减少和结点漏电流的增加,从而降低器件性能、可靠性甚至失效;

在生产过程中,铜在空气和低温环境下(<200℃)比较容易氧化,而且不能像锌和镍一样形成至密保护层来阻止进一步氧化和腐蚀;

铜对氧化硅等介质材料的附着性较差,极易剥离脱落。然而,功率半导体需要的绑定线比较粗,也就要求表面金属化需要一定的厚度以保证绑定过程各种能承受更大的压力和功率,就是所谓厚铜工艺。厚铜反而会导致更加严重剥离问题。

生产设备昂贵,想积淀一定厚度的铜原子层很困难,成本非常高。特别是厚铜工艺,就更加困难了。

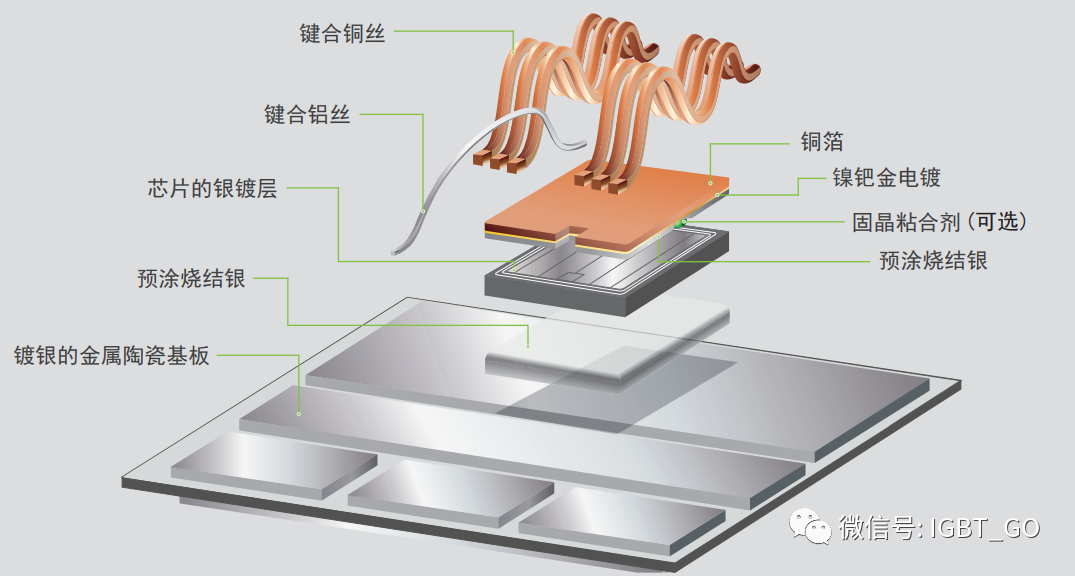

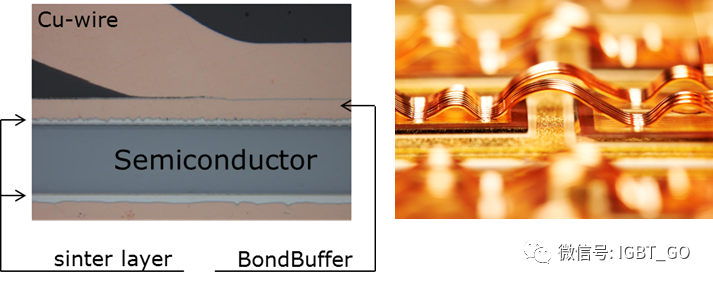

目前在功率半导体领域,我们知道实现芯片表面铜金属化以及铜绑定线工艺并量产的只有英飞凌。在其IGBT5,PrimePACK封装产品上导入了铜绑定线工艺,其所谓的.XT技术。上图是英飞凌在其论文中给出的对比示意图。作为行业大佬在工艺上还是很有实力的。从上面的图上看,铜与绝缘层之间貌似还有一层的(浅灰色)。不知道这一层是采用了何种工艺,不过也应该是为了解决上述的一些工艺问题而采用的措施。Danfoss BondBuffer介绍

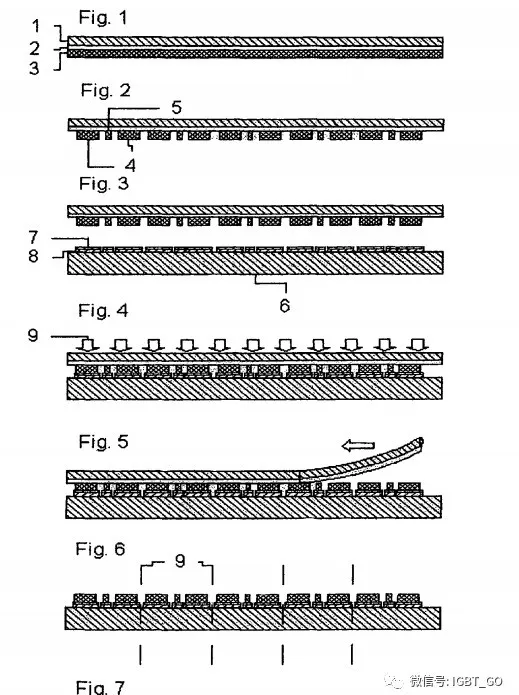

Danfoss BondBuffer(DBB)。所谓的DBB,字面意思理解就是绑定缓冲层。前面的介绍也可以知道,对于铜绑定线工艺来讲,困难和问题不在绑定线本身,而在于芯片表面需要通用使用铜才能实现铜绑定线的工艺。而铜绑定线就是打在这个Buffer层上,意味着芯片表面并没有采用铜金属化工艺,从而去避免上述各种问题。对于该技术我查阅到丹佛斯申请了不多的核心专利,主要在于工艺过程:直接在晶圆上贴附Buffer铜层以及烧结材料;将带着Buffer铜层但是并未烧结的芯片放置到DBC上;然后上下一起一次烧结成型的这样一个完整过程,下面附两张专利文件的说明图,基本揭示了这一工艺的过程和特点(美国授权专利号为:US20140230989A1;中国专利号为:CN103875067A)。

首先是有这个一个整体的Buffer铜层(3),如下图所示,固定在一个支架上(1),根据芯片在晶圆上的分布和外形将Buffer铜层做出跟芯片对应的外形。芯片(6)表面预涂烧结银复合层(7),然后将Buffer层放置在晶圆上压紧。然后再撤去支架。

如上图所示,在晶圆上处理完成后需要把芯片从晶圆上取下来放置到DBC上,如下图所示完成芯片(2)在DBC上的集成,然后再进行整体的烧结工艺。同时芯片表面就具有了相当厚的铜金属化层。然后再去进行铜绑定线的连接工艺。

上面专利中的缓冲层工艺是最早丹佛斯申请的专利,后面有所改进。这里就不再展示了。

这里的DBB技术跟贺利氏所推的Die Top System (DTS) 属于同一种方案,二者应该是专利交叉授权实现技术共享的,但是我没有查询到贺利氏在这方面相关的专利,贺利氏的专利主要是在烧结工艺,基础材料,绑定线等方面。猜测可能是贺利氏在烧结工艺以及Buffer材料方面有一些专利壁垒,同时也是这方面领先的供应商,而且开发过程中互有合作,因此双方达成了交叉授权协议。在贺利氏网站上找到了关于该技术的声明如下:

贺利氏与丹佛斯公司(Danfoss)在Danfoss BondBuffer®技术方面建立了合作关系。贺利氏Die Top System可能涉及到Danfoss和贺利氏的某些知识产权,详情请参阅《客户声明》(Declaration to Customers)。

贺利氏

丹佛斯的宣传资料中也有一张图展现了采用DBB技术的铜绑定线的切面图,如下图所示。可以看出,Buffer层的厚度还是非常厚的。跟芯片表面的金属化层厚度不在一个量级,应该会在几十个um以上。这样去打铜绑定线是完全可以承受更高的压力和功率的。

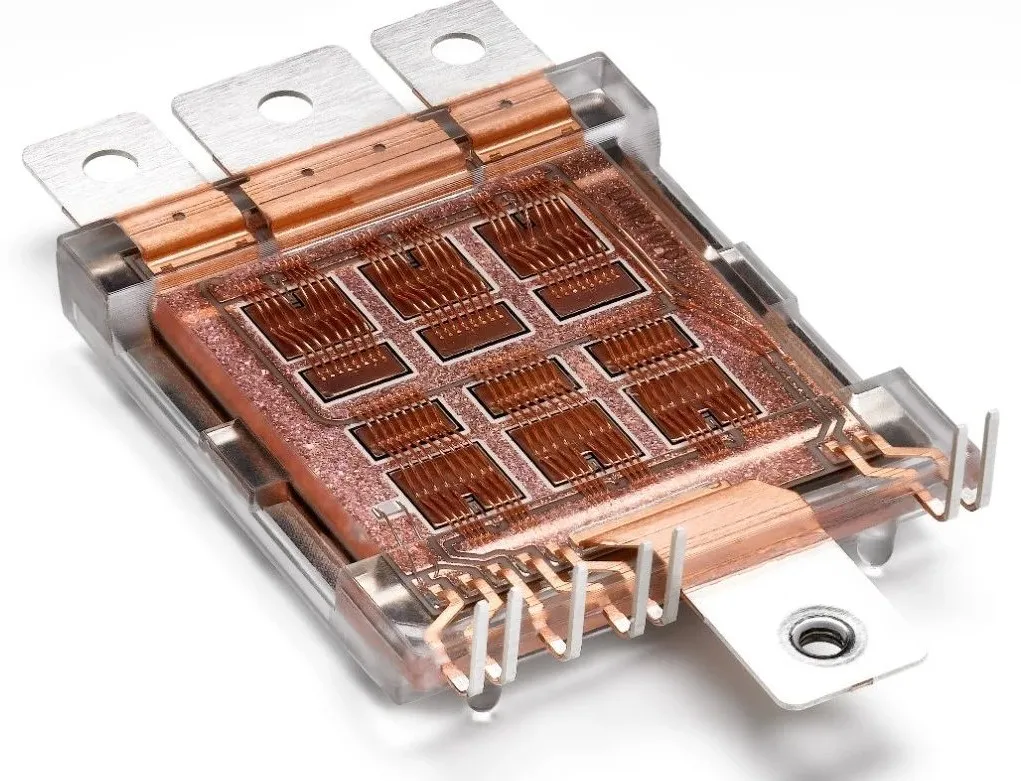

DCM™-采用DBB工艺的产品的特点

前面介绍了DBB的实现过程以及工艺。下面介绍一下应用这种工艺的产品DCM™平台的车规级IGBT模块采用铜绑定线的特点。

寿命可靠性提升,功率循环能力增强;

降低内部阻抗;

减小热阻;

改善焊层老化以及空洞问题

改善芯片表面电流分布;

改善芯片表面温度分布

支持更高的工作结温。

下面主要介绍几个重要的或者说有意思的点。第一个是功率循环能力的提升;第二个是芯片表面温度分布的改善;第三个是芯片表面电流分布的改善。

1,功率循环

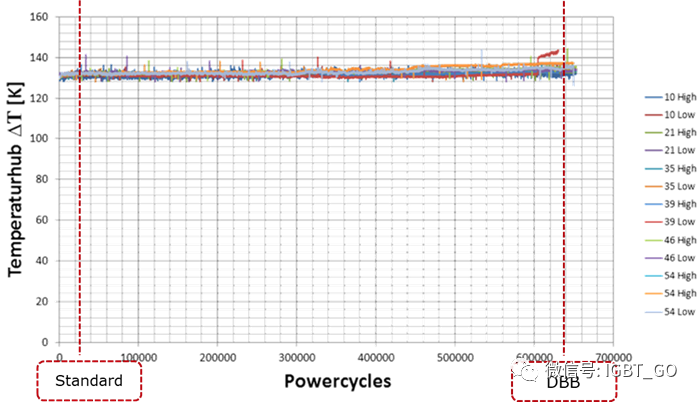

我们提功率循环能力的时候往往绑定线是一个主要的考察点。丹佛斯在其宣传材料中给出了下面的一个PCsec测试图,PCsec主要是考察绑定线,PCmin主要是底部连接。烧结工艺对底部连接的改善也有很多讨论,这里主要说说这个PCsec的测试结果。用6只采用DBB技术的模块来跑功率PCsec, ΔT是130℃,其他测试条件没有说明。在同等条件下,采用DBB技术的模块的功率循环能力可以提升30倍(630k/21k)。这可以说是非常强的一个数据了。

当我们把DBB铜绑定线的模块与普通模块对比,如下图,就可以发现,在更高结温的时候普通铝绑定线的模块功率循环能力是极为有限的,甚至只有数万次,也就是说在高工作结温的时候,寿命是有限的。这样就会极大的限制其工作结温的提升,或者只能在控制一定次数之内。而采用DBB技术之后,功率循环能力得到一个极大的提升,ΔT在130℃左右的时候的功率循环能使与普通模块ΔT在60℃左右的时候是类似的。这样就可以说改善了更高工作结温的限制。如其在规格书中所标注的,工作结温可以做到175℃,同时寿命也得到保证,甚至在不用考虑寿命计算。

2,芯片面温度分布的改善

这一点还是比较有意思的。丹佛斯在其宣传资料中给出了下面这一组测试对比图,左边的是没有采用DBB技术的普通模块的芯片表面热分布;右侧是在同等结温(Tvj)条件下,采用DBB技术的芯片的表面热分布。图中给出了两者最高温度,竟然相差了11℃。意在说明,得益于芯片表面厚铜层的优异的导热性能,芯片的温度分布更加均匀。下面我做了一个示意图,其中红线代表芯片表面横向的温度分布,橙色曲线代表芯片的平均结温(数值是我猜的,资料中没有给出),可以看出左边的芯片表面温度分布梯度更大,因此最高结温更高;右侧的温度梯度更加平缓,最高结温也相对较低。

我们一般称呼的结温Tvj并不是芯片的最高温度,而实际上这是指的一个“平均值”(对于多个芯片并联的模块也是一样),此时芯片的最高温度是要高于Tvj的,就像上面图片中一样。尤其是当工作结温非常高的时候,梯度会更大,而高温又是威胁芯片性能和可靠性的一个重要因素,应该也是限制工作结温提升的一个因素。DBB技术对芯片表面温度分布的改善这一点,对于其产品在保证可靠性的前提下提高工作结温(Tvjop=175℃)应该也是起着非常重要的作用。

此外个人认为还有一点就是对“结温过高(over junction temperature)”这种失效模式的改善。我们知道,一般结温过高失效一般是一个非常短暂的瞬态过程,可能是由于驱动故障,或者短路等原因造成开关损耗增大很多并导致结温的急剧升高。这种失效一般产生的失效特征是芯片表面铝层的融化,如下图所示,严重的甚至会熔融成球状物。而我们知道,铜是非常好的热导体,那么DBB烧结在芯片上面的Buffer铜层有几十个um,相对于芯片表面几个um的铝层,可以说是非常好的散热体了。而且其优异的热阻容特性有非常好的吸热性能以降低芯片表面的瞬间温升,从而改善这个问题。

3,芯片表面电流分布的改善

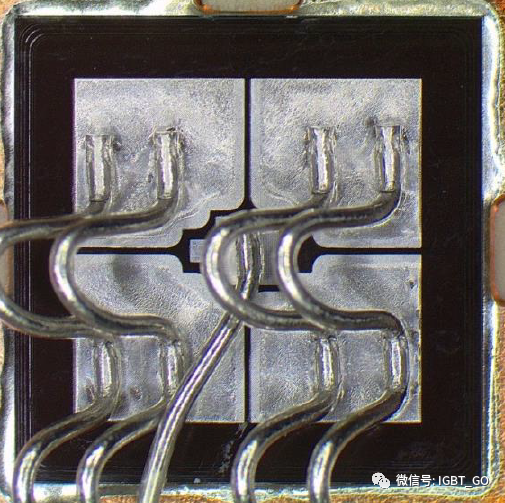

这一点在丹佛斯的宣传资料里有提到,但是没有详细的介绍。我们知道一般芯片表面会进行一层金属化层,来将元胞连接在一起,算是汇流的作用。然而实际上这一层金属化层是非常薄的,也就几个um。面对单个元胞其载流能力还是可以的,但是面对很多元胞电流汇聚在一起,通过绑定线流出的时候,绑定线下面的铝层其实是芯片载流能力的瓶颈所在了。这自然就引出了一个现象就是,芯片过流失效,或者脉冲电流失效的时候(脉冲电流失效其实司非常有意思的一个模式,在传统功率器件中失效现象非常典型),由于绑定线下面的铝层较薄,相对阻抗较大,因此失效的时候绑定线下面会发生熔融现象,如下图所示。可以看出其特点是当绑定线下面的连接点完全融化甚至脱落了,芯片其他位置的表面铝层依然良好没有熔融现象。

前面也提到,DBB的这个Buffer层有几十个um的厚度。通过下图可以看出,相对于绑定线来说已经很厚了。这个厚度对于汇集到绑定线的电流来说阻抗应该很小,载流能力大大加强。因此在应对突发的大电流或者脉冲电流的时候,绑定线下面的点可能并不会首先过热熔融!这就意味着这一个可靠性的短板被加长了,可以承受的过电流或者脉冲电流能力得到了质的提升。当然短路能力也可以说是有所提升。

总结

丹佛斯DBB技术在解决功率半导体铜绑定线问题上应该说是一个非常具有创意的方案。在解决绑定线寿命问题,提高工作结温等方面有着比较好的表现。与此同时,对可靠性的其他一些方面,比如过温能力,过流能力等也有着不错的改善。

当然这种工艺不是没有缺点,比如对芯片上下表面需要特殊的处理以满足烧结的要求;整个生产流程的设备,供应链应该都需要特殊设备以及原材料,这必然影响其成本。如果这种产品做下来价格太高,虽然具有性能、可靠性的优势,但是在可靠性要求不是很高的场合,未必具备很强的优势。当然电动汽车领域的应用应该说还是非常有吸引力的,其实现在来看的话,已经在市场上看到了除了丹佛斯之外国内的客户在从贺利氏采购这个方案了。

最后另外从长远发展来看的话,笔者认为DBB工艺在225℃结温以下是极具有竞争力的,特别是在SiC的应用上,极具潜力。不过如果SiC模块的结温进一步提高的话,DBB包括Clip绑定可能会面临和双面冷却类似的需要牺牲芯片有效区域面积的问题。

原创文章,转载请注明出处:http://mysic.cn/blog/article/dbb/